底部填充工藝:先進封裝可靠性的關鍵工藝

發布時間:2025-12-20 13:52:55 瀏覽:1179次 責任編輯:騰盛精密

在半導體封裝技術飛速發展的今天,底部填充工藝已成為確保芯片長期可靠性的核心技術之一。隨著芯片集成度不斷提升、封裝尺寸持續縮小,熱膨脹系數(CTE)失配導致的應力問題日益突出,底部填充工藝應運而生并不斷發展,成為先進封裝技術中不可或缺的關鍵環節。

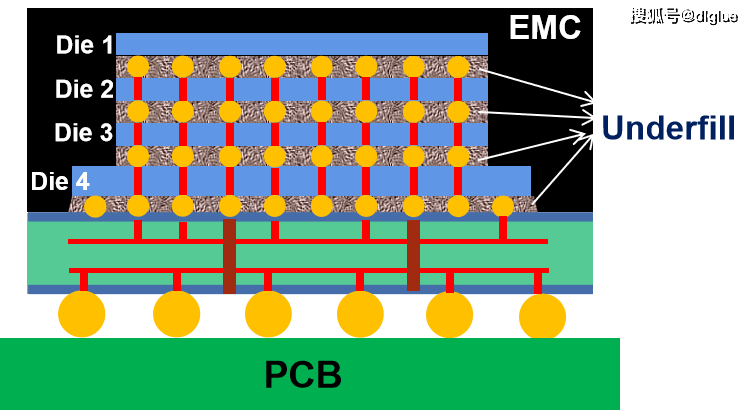

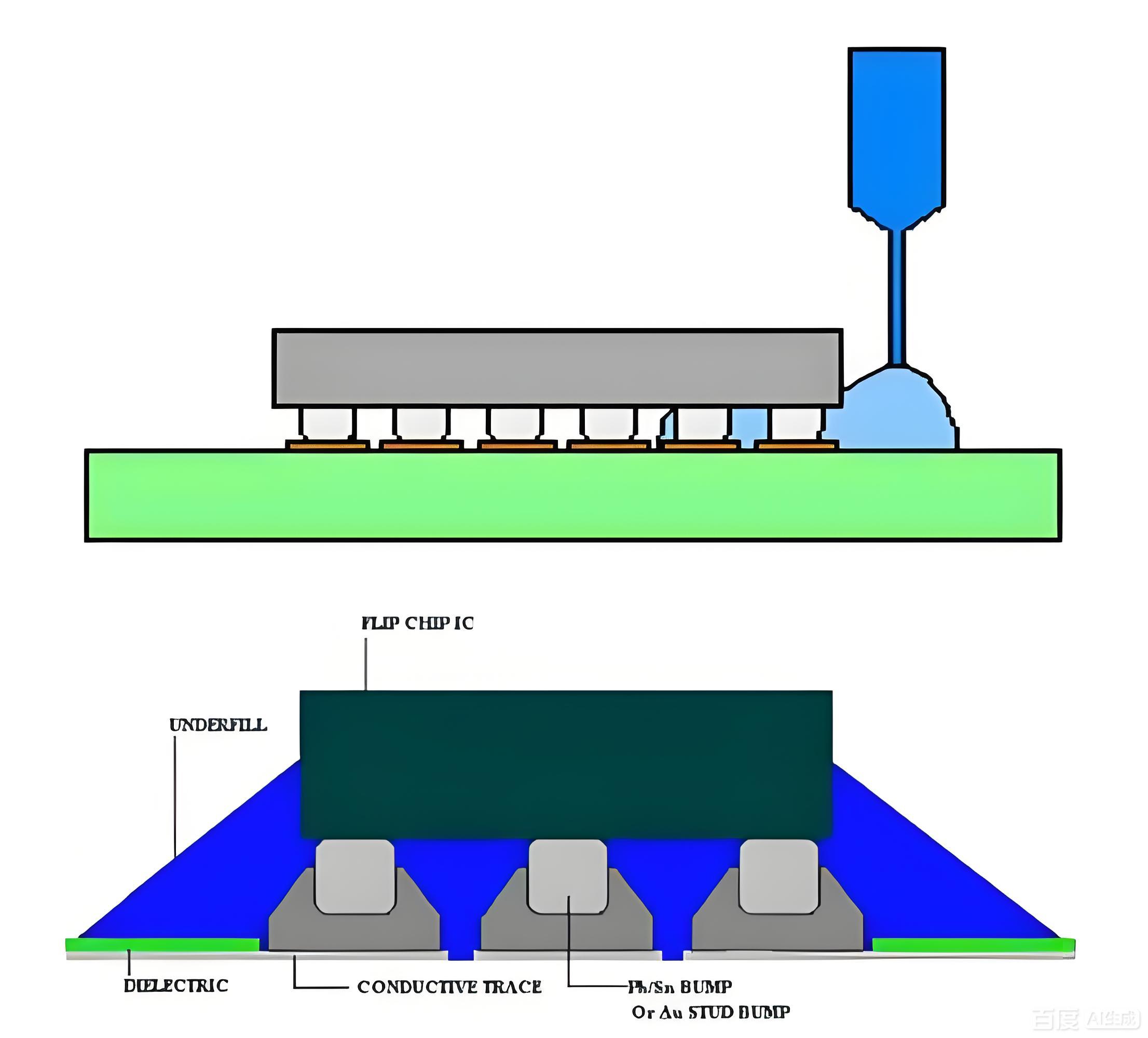

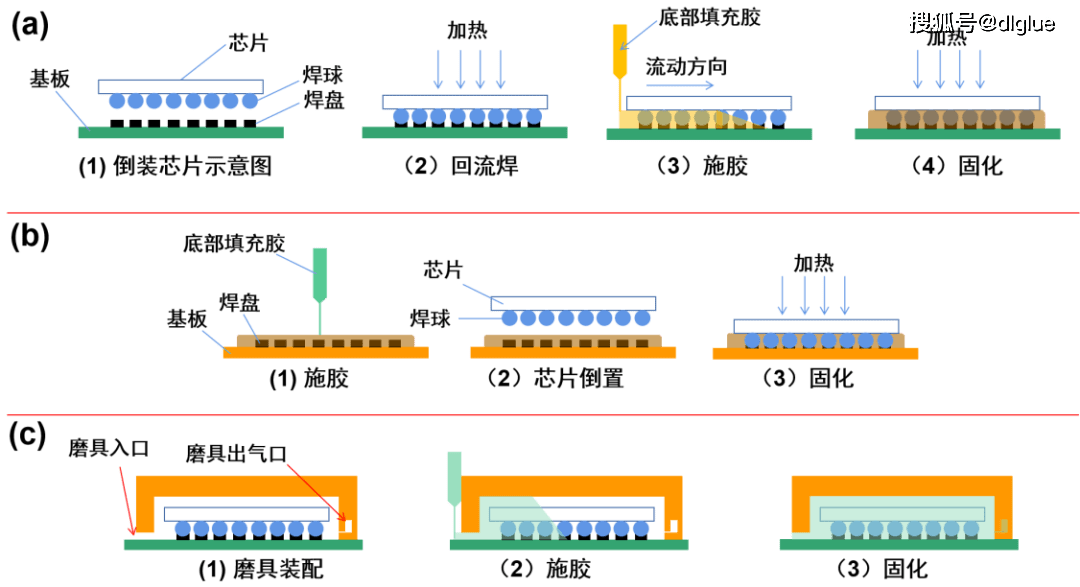

▲底部填充工藝示意圖 來源:網絡工藝背景與發展現狀

▲底部填充工藝示意圖 來源:網絡工藝背景與發展現狀

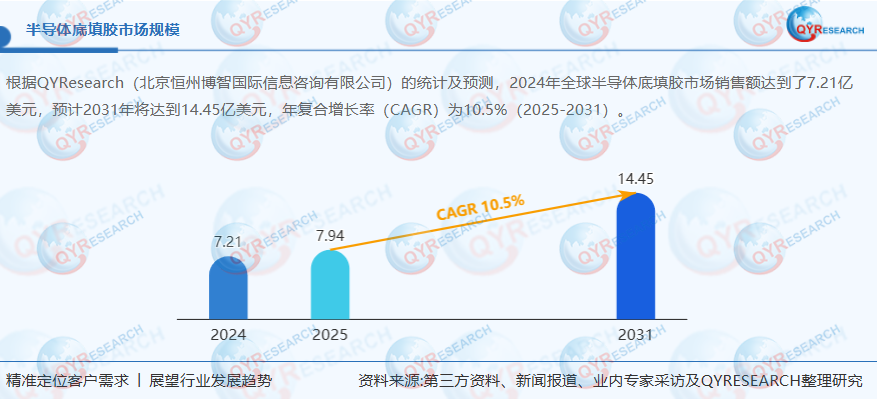

半導體底部填充技術起源于20世紀70年代的IBM公司,最初應用于陶瓷基板領域,后隨著有機基板取代陶瓷基板而實現規模化應用。全球半導體底部填充膠市場預計以10.48%的年復合增長率(CAGR)持續擴張,2024年市場規模達7.21億美元,2031年將突破14.43億美元。中國市場表現尤為突出,預計2031年全球占比將達24.72%,增速顯著高于全球平均水平,這主要得益于新能源汽車、AI芯片、5G通信等新興技術領域的快速發展。

▲全球半導體底部填充銷售額 來源:網絡工藝原理與核心價值

▲全球半導體底部填充銷售額 來源:網絡工藝原理與核心價值

底部填充工藝的核心原理是通過在芯片與基板之間填充高分子材料,形成機械支撐結構,有效分散因熱膨脹系數差異產生的應力。具體而言,當芯片與基板經歷溫度變化時,固化后的底部填充材料將兩者緊密連接,使原本集中在焊點上的應力重新分布到整個界面區域,從而顯著降低焊點所承受的應變。

底部填充工藝提供三大核心價值:

· 應力緩沖與分散:緩解CTE失配導致熱機械應力,防止焊點疲勞開裂

· 增強機械強度:為焊點提供額外支撐,提高抗沖擊、抗振動能力

· 環境防護:形成密封屏障,防止濕氣和污染物侵入,避免腐蝕和短路

▲底部填充工藝示意圖 來源:網絡工藝類型與技術分類

底部填充工藝主要分為以下幾類:

1. 按填充方式分類

· 毛細流動型底部填充(CUF):依賴膠水毛細流動自然填充,工藝簡單但耗時較長

· 非流動型底部填充(NUF):預先點膠后通過回流焊固化,適用于CSP、BGA等工藝

· 晶圓級底部填充(WLUF):在晶圓制造階段完成填充,適合超薄芯片

· 模塑底部填充(MUF):結合注塑成型工藝,適用于多芯片集成封裝

▲底部填充工藝分類 來源:網絡

2. 按應用場景分類

· 倒裝芯片底部填充:用于芯片與封裝基板互連凸點之間間隙的填充,精度要求高(微米級)

· BGA底部填充:用于封裝基板與PCB印制電路板之間互連的焊球之間的填充,精度要求相對較低(毫米級)騰盛精密底部填充解決方案

底部填充工藝作為半導體封裝中的關鍵環節,雖然能顯著提升器件可靠性,但在實際應用中仍面臨多重技術挑戰,主要包括填充不飽滿、空洞形成、材料匹配、熱管理、大尺寸芯片封裝等核心難點。作為國內領先的精密裝備企業,騰盛精密針對不同封裝需求開發了專業化的底部填充設備:

1、晶圓級底部填充WDS2500

· 技術特點:定制專屬的設備前端模塊,1供2的配置與2臺點膠機組成完整系統

· 兼容性:可兼容8/12英寸晶圓,設有預熱平臺和冷卻平臺

· 應用場景:專為晶圓級Underfill工藝研發,適用于CoWoS等先進封裝技術

2. 面板級底部填充Sherpa1000

·技術特點:專為面板級工藝研發,支持大面積模塑

·核心優勢:可實現2-3倍的產能提升,有效緩解AI芯片對先進封裝產能的瓶頸

·應用場景:適用于CoPoS等先進封裝技術,滿足高密度、大面積封裝需求

3. 板級底部填充Sherpa900

· 技術特點:采用一體式鑄造成型工藝,搭載龍門雙驅U型直線電機,點膠快準穩

· 核心優勢:支持選配傾斜旋轉機構,實現芯片四邊的傾斜點膠,對于提升Fillet,減小KOZ效果顯著

· 應用場景:適用于FCBGA、FCCSP、SiP等封裝中的倒裝技術

在半導體產業向高性能、小型化、高可靠性發展的今天,底部填充工藝作為封裝可靠性的關鍵保障,其技術進步將直接影響半導體產品的性能與壽命。隨著中國企業在Chiplet封裝等領域的持續突破,本土品牌在全球高端市場的份額有望逐步提升,為半導體產業鏈的自主可控發展提供有力支撐。

深圳市騰盛精密裝備股份有限公司

深圳市騰盛精密裝備股份有限公司